- Sectores

- Aeroespacio y defensa

- Biotecnología

- Fintech

- Industria de la ciencia

- Sobre ARQUIMEA

- Trabaja en ARQUIMEA

La complejidad cada vez mayor de los sistemas espaciales está creando la necesidad de tecnologías de redes fiables de alta velocidad para la interconexión de los distintos elementos de las naves espaciales. Ethernet, al haberse adoptado tan ampliamente en aplicaciones terrestres, se está empleando en el ámbito espacial y se está normalizando para cumplir con las necesidades de las diferentes aplicaciones, sobre todo aquellas en las que se considera importante una mejor calidad de servicio, la sincronización a prueba de fallos y las comunicaciones deterministas en tiempo real.

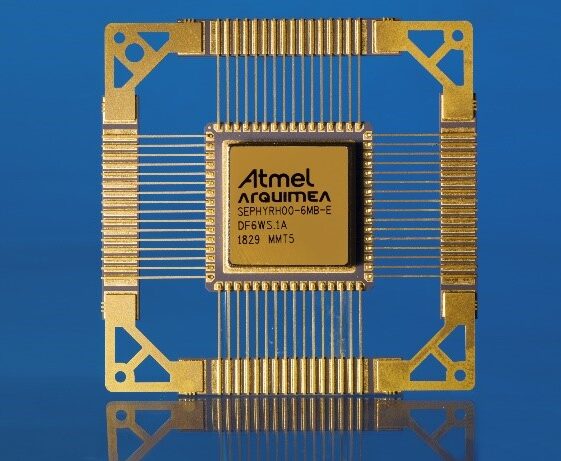

SEPHY, un transceptor de Ethernet de aplicación espacial, permite adoptar plenamente los protocolos de comunicaciones requeridos en las aplicaciones espaciales a la vez que mantienen la interoperabilidad con las normas técnicas existentes. SEPHY tiene como objetivo aumentar la competencia europea mediante la propuesta de un transceptor PHY (de capa física) de Ethernet 10BASE-T/100Base-TX resistente a la radiación que no aplica los reglamentos sobre tráfico internacional de armas (ITAR, por sus siglas en inglés). Es el primer PHY de Ethernet resistente a la radiación disponible en el mercado y está destinado tanto a aplicaciones espaciales (lanzaderas, satélites, nave espacial) y terrestres en los casos en que un entorno de alta radiación o la alta fiabilidad sean una preocupación.

El programa europeo H2020 ha financiado el proyecto, abordando la necesidad de que Europa no sea dependiente en las tecnologías esenciales, lo que convierte a Europa en pionera en estos importantes componentes electrónicos espaciales. El equipo del proyecto estuvo formado por ARQUIMEA (en calidad de coordinadora y responsable de las actividades de diseño), IHP Microelectronics (que llevó a cabo funciones de diseño digital), la Universidad Antonio de Nebrija (asistencia a las actividades de diseño), Microchip (proveedor de la tecnología microelectrónica ATMX150RH), Thales Alenia Space España (caracterización eléctrica y ensayos de radiación) y TTTech, usuario final del chip.

El desarrollo del transceptor PHY de Ethernet 10BASE-T/100Base-TX para el espacio exigió establecer la mejor estrategia en cuanto a la implementación del dispositivo mediante la adaptación de los requisitos del estándar comercial Ethernet IEEE802.3 a las necesidades espaciales y la prioridad de los aspectos más importantes para conseguir fiabilidad y una resistencia a la radiación mejorada.

La coordinación de un consorcio europeo en un proyecto tan innovador en el que no se estableció ninguna directriz formal para el uso de Ethernet en el espacio, junto al hecho de que cada entidad tiene su propia experiencia y manera de proceder, hizo necesario un gran esfuerzo comunicativo, una formación técnica y un análisis de mercado, así como el poder de persuasión para adoptar los mejores compromisos durante la implementación.

El desarrollo de un producto complejo como SEPHY, basado en el estándar comercial Ethernet IEEE802.3, no solo depende de su materialización (punto de equilibrio entre el diseño resistente a la radiación y sus prestaciones), sino también de una comprensión correcta de los requisitos de las diferentes aplicaciones objetivo y del mercado correspondiente. La participación del grupo de trabajo de la ESA en el estándar Ethernet para el espacio, así como de los diseñadores de las capas OSI de mayor nivel, como TTTech, y los usuarios finales, como Thales Alenia Space, permitieron establecer unos objetivos reales y las necesidades del mercado.

DISEÑO

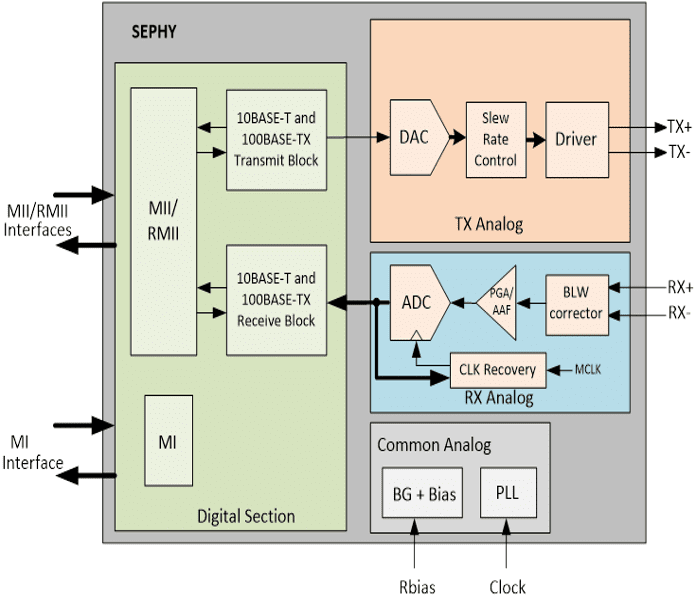

La definición de las exigencias de diseño dependió de las competencias concretas de cada miembro del consorcio. Las características principales fueron la compatibilidad con el estándar ANSI X3.263-1995, la circuitería de recuperación del reloj integrado de 100 Mbps que no requería de filtros externos, el soporte full-duplex, los modos de bucle de retorno programables para diagnósticos sencillos del sistema, la interfaz de comunicación MAC MII/RMII y MI para la gestión y el diagnóstico del módulo MAC.

El desarrollo se basó en dos ciclos de fabricación, lo que permitió mejorar las prestaciones analógicas mediante la validación de un chip de prueba con los bloques analógicos fundamentales. La aplicación de técnicas de mitigación de resistencia a la radiación en la parte analógica permitió complementar las características de resistencia a la radiación ofrecidas por la tecnología CMOS-SOI (semiconductor complementario de óxido metálico-silicio sobre aislante) ATMX150RH y la biblioteca asociada.

IMPLEMENTACIÓN Y VALIDACIÓN

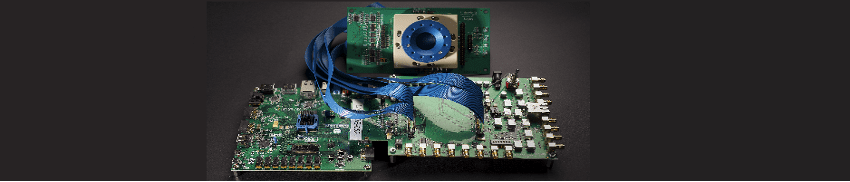

Las actividades de fabricación de las obleas las llevó a cabo MICROCHIP conforme a la tecnología CMOS-SOI ATMX150RH. Los dispositivos se montaron en un paquete CQFP-64 hermético de cerámica. La caracterización eléctrica y los ensayos de radiación los llevó a cabo Thales Alenia Space con una configuración que integra FPGA Xilinx para reproducir el funcionamiento típico y emular la red TTEthernet. La misma configuración utilizada con radiación de iones pesados permitió medir la BER (reparación de escisión de bases) bajo diferentes escenarios de radiación.

CONSULTAR Configuración de la prueba de SEE