- Sectores

- Aeroespacio y defensa

- Biotecnología

- Fintech

- Industria de la ciencia

- Sobre ARQUIMEA

- Trabaja en ARQUIMEA

Las FPGA basadas en flash son relativamente productos nuevos dentro de la cartera de FPGA de aplicación espacial, y el flujo de desarrollo conforme a las exigencias espaciales no ha sido probado aún en su totalidad mediante un amplio aprendizaje y una dinámica de retroalimentación con los clientes.

Aunque no ha sido desarrollado inicialmente para un entorno espacial hostil, la FPGA basada en flash de tercera generación de Microsemi, conocida como IGLOO2 y PROASIC3, se utiliza ampliamente en aplicaciones espaciales gracias a la resistencia a la radiación de la configuración basada en flash y a la implantación de una técnica de diseño específica contra los efectos de la radiación. La cuarta generación (RT Polarfire y RTG4) destinada a aplicaciones espaciales convencionales, como los ordenadores de alto rendimiento a bordo y la carga útil de procesamiento de datos de ancho de banda alto, ya se aplica en recursos programables de alto rendimiento resistentes a la radiación, memorias digitales, bucles de seguimiento de fases (PLL) e interfaces de entrada y salida. La ejecución automática de las técnicas de mitigación de SEU (alteraciones de evento único) y el filtro de SET (transitorio de evento único) es posible a través de las herramientas de síntesis y place and route, respectivamente.

Al ser relativamente nuevos, estos dispositivos cuentan con antecedentes espaciales y datos relativos a la radiación muy escasos en comparación con otras soluciones más maduras como es la familia de antifusibles RTAX de Microsemi. La implantación adecuada de técnicas de mitigación SEU y SET es difícil de confirmar y verificar de forma automática y rigurosa, ya que las herramientas de verificación formal de la automatización de diseño electrónico (EDA, por sus siglas en inglés), como Synopsys Formality y Mentor Formal Pro, no pueden confirmar la equivalencia lógica de un diseño resistente a la radiación frente a su homólogo sin mitigar, ni verificar la implantación adecuada en las áreas especificadas. Esto podría conducir a posibles deficiencias de diseño y a fallos imprevistos bajo la radiación. Por otro lado, estudios anteriores realizados por Airbus Defense & Space en colaboración con el GSFC de la NASA han mostrado sensibilidad a la radiación de SEE en el tejido de la FPGA RTG4 y la capacidad de reprogramación de celdas de configuración.

Para entender mejor las FPGA basadas en flash de tercera y cuarta generación de Microsemi y su rendimiento frente a la radiación, la ESA emitió un contrato a ARQUIMEA con los objetivos siguientes:

La actividad exigió el desarrollo de varios vehículos de pruebas complejas en la FPGA RTG4 para validar el impacto bajo una intensa radiación de iones y protones del tejido de la FPGA y diseños mitigados SEU y SET comparados con sus homólogos sin mitigar. Igualmente, se tuvieron en cuentas las limitaciones de planificación y el posible daño de las FPGA RTG4 por operaciones de rectificado o fallo eléctrico como los riesgos principales del proyecto.

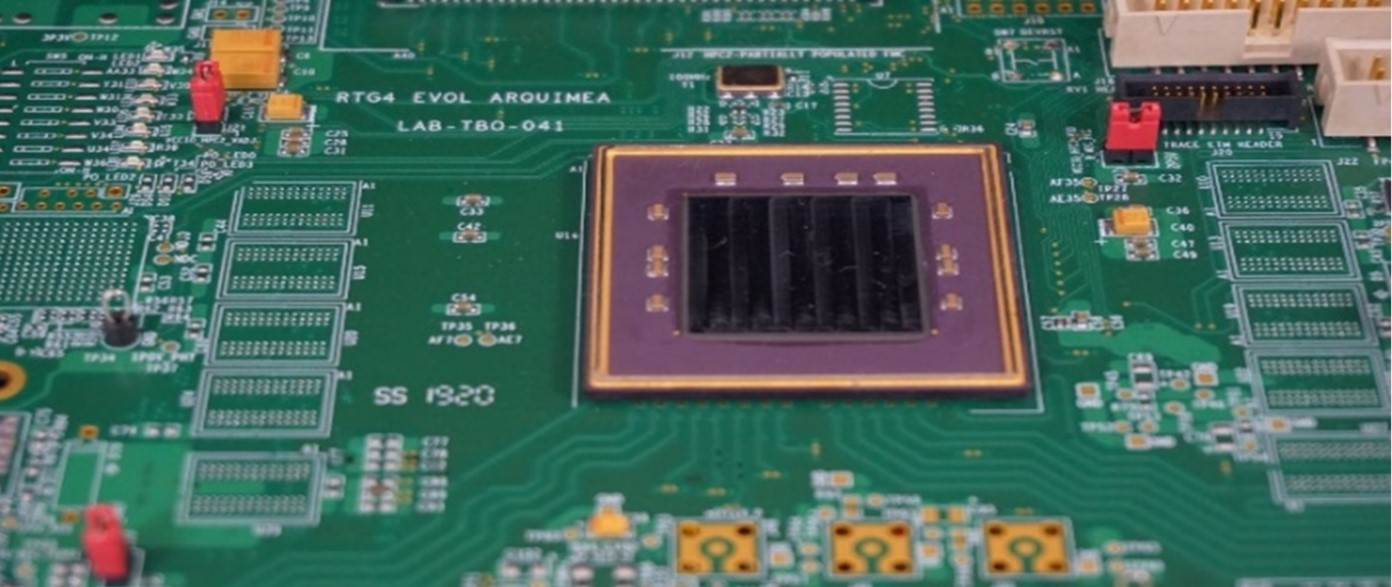

ARQUIMEA dirigió un consorcio que llevó a cabo el diseño de circuitos integrados resistentes a la radiación en funcionamiento en el RTG4, así como las herramientas de verificación para probar la equivalencia de los diseños con y sin técnicas de mitigación de SEE. Los dispositivos se validaron bajo radiación utilizando la configuración de las pruebas de SEE propia de ARQUIMEA.

DISEÑO DE VEHÍCULO DE PRUEBAS DE RESISTENCIA A LA RADIACIÓN

La validación de una tecnología contra la radiación requiere del cuidadoso análisis de los datos disponibles de actividades anteriores de caracterización, como es el caso del FPGA RTG4, para elaborar primero un plan estratégico para la obtención de los resultados complementarios más valiosos y permitir destacar las posibles deficiencias latentes en un entorno de radiación. El enfoque se basa en los Circuitos de Evaluación Dinámica (DEC, por sus siglas en inglés), que incluye estructuras como los registros de Desplazamiento de Ventanas, Osciladores de Anillo, Interfaces de Entrada y Salida, POR, SERDES, PLL, etc. con ligeras variaciones entre ellas (filtro SET, tamaño lógico, diseño de reloj de árbol, PLL int/ext, etc.), para caracterizar los llamados recursos de tejido y poder cubrir los aspectos tecnológicos. Los Circuitos de Evaluación Representativos (RIC [sic], por sus siglas en inglés) incluyen núcleos IP como ARM M0, SpW Codec, CCSDS121 o bus CAN (Red de Área Controlada) y complementan los resultados de los DEC, lo que permite un mejor entendimiento del impacto de las técnicas complementarias de mitigación SEU personalizadas. Se propusieron varias frecuencias, la polarización o el modo de funcionamiento bajo radiación para evaluar la influencia en las condiciones de los ensayos.

CONFIGURACIÓN DE LAS PRUEBAS DE SEE

La configuración de ARQUIMEA está controlada y monitorizada a través de un ordenador que ejecuta el software RTCAS propiedad de la empresa. El ordenador está conectado al hardware a través de una conexión de Ethernet, comúnmente disponible en instalaciones con radiación. La configuración del hardware es modular y tiene una placa base que implementa los FPGA Smart Fusion 2 y una serie de placas secundarias.

Se lleva a cabo una autocomprobación del sistema para analizar su comportamiento correcto antes de que comience la prueba de radiación. La placa base sujeta los conectores principales al resto de las PCB (placas de circuito impreso) y contiene la lógica utilizada para el control de la temperatura, la configuración de la fuente y la detección de bloqueo. La placa secundaria permite controlar y hacer el seguimiento de más de 800 pines con una frecuencia por encima de 400 MHz. Al menos dos de las placas base supervisan el conteo de la configuración y detección de SEU y SEFI (interrupciones funcionales de evento único).

Las FPGA RTG4 se instalaron en placas DUT (dispositivo sometido a prueba) separadas y pudieron conectarse fácilmente al sistema. En función del tamaño del chip y la distribución de los pines, pudieron instalarse varias DUT en una placa secundaria. Esto permite ahorrar tiempo al evitar que la manipulación de la placa durante las pruebas de radiación. Para los ensayos de protones, se separaron las placas DUT de la placa secundaria con cableado y apantallamiento adecuados para evitar la degradación electrónica.

Configuración de las Pruebas de SEE de ARQUIMEA

Se llevaron a cabo dos campañas de SEE en el FPGA RTG4 bajo iones y protones pesados en noviembre de 2019. Las mediciones confirmaron los resultados de Microsemi y el GSFC de la NASA. No obstante, se observaron los comportamientos siguientes: