- Sectores

- Aeroespacio y defensa

- Biotecnología

- Fintech

- Industria de la ciencia

- Sobre ARQUIMEA

- Trabaja en ARQUIMEA

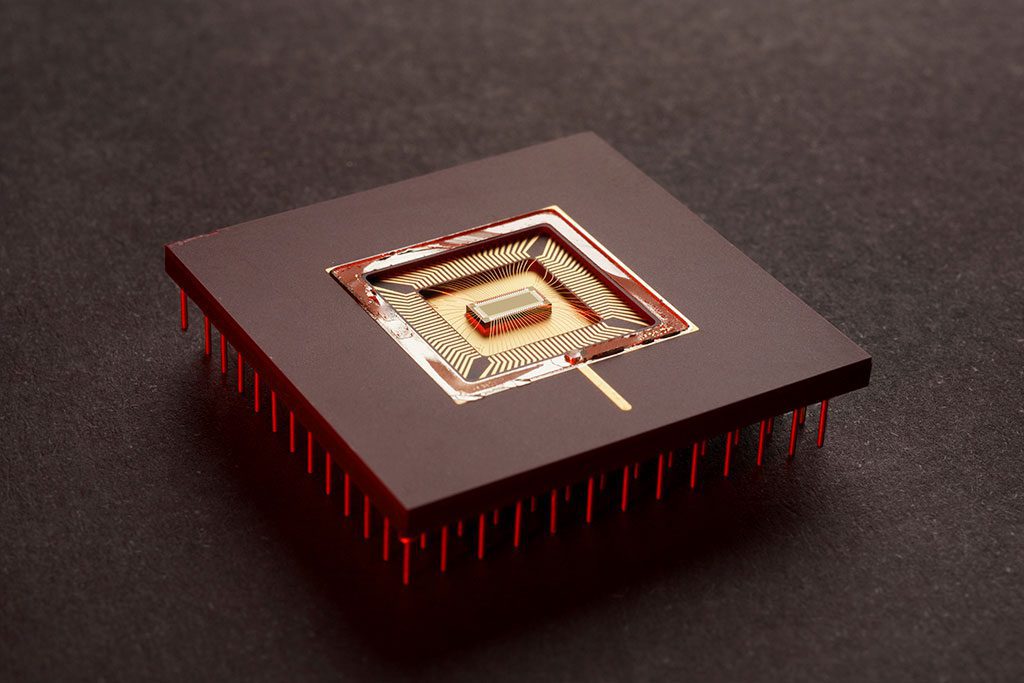

Proporcionamos microelectrónica analógica, digital y de señal mixta, incluyendo núcleos IP, ASIC, FPGA, ASSP y componentes estándar. Ofrecemos soluciones integrales, desde la definición de requisitos, el análisis de viabilidad y la selección de tecnología hasta el diseño, la fabricación y la calificación de chips según los estándares espaciales.

Nos especializamos en circuitos integrados basados en tecnologías comerciales y endurecidos por diseño contra los efectos de la radiación cósmica y ambiental.

Proporcionamos la tecnología más adecuada para cada aplicación: alta tensión, alta velocidad, baja potencia… Nuestra experiencia va desde nodos maduros hasta submicrones profundos (22nm e inferiores).

Nuestros desarrolladores de microelectrónica espacial crean sistemas capaces de cubrir las exigentes necesidades y prestaciones de las misiones espaciales, para que resistan las complejas condiciones durante el proceso de lanzamiento y funcionar de manera fiable en las adversas condiciones de radiación del espacio.

Contacta con nosotros, plantéanos un reto y descubre todo lo que podemos ofrecerte.